Product Summary

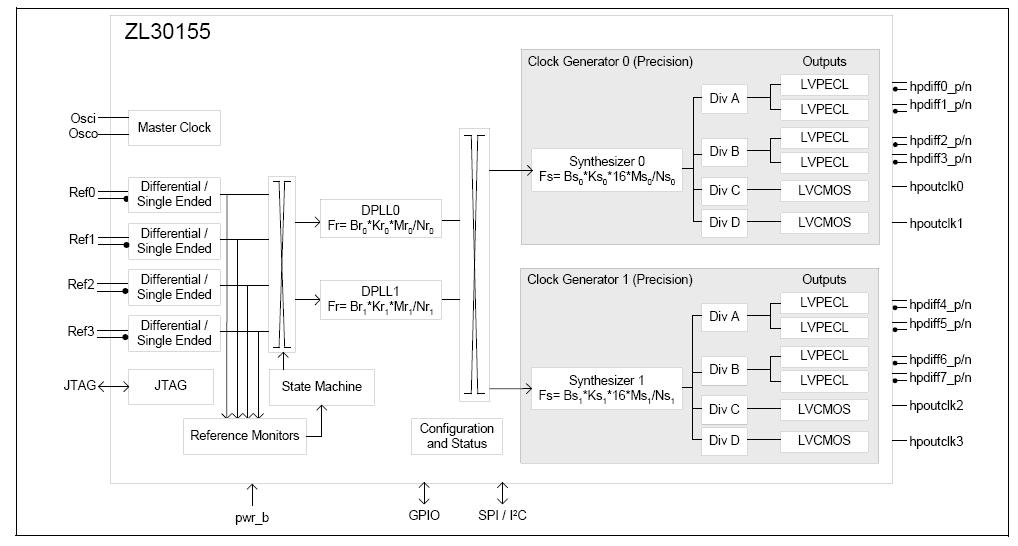

The ZL30155 is a Dual Channel Universal Clock Translator. It delivers industry leading synchronization performance for high-speed complex applications. The highly integrated and programmable solution provides translation from any input reference frequency to any output clock frequency with jitter performance that can directly drive 10G PHY devices. The ZL30155 integrates 2 independent digital PLLs, accepts 4 input references and generates 12 programmable clock outputs. The highly integrated solution allows designers to replace multiple components with a single chip, simplifying design and reducing component count and power. The applications of the ZL30155 include 10 Gigabit linecards, Synchronous Ethernet, 10GBASE-R and 10 GBASE-W, OTN multiplexers and transponders, SONET/SDH, Fibre Channel, XAUI.

Features

ZL30155 features: (1)Two independent clock channels; (2)Programmable synthesizers generate any clockrate from 1 kHz to 720 MHz; (3)Two precision synthesizers generate clocks with jitter below 0.7 ps RMS for 10 G PHYs; (4)Programmable digital PLLs synchronize to any clock rate from 1 kHz to 720 MHz; (5)Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates; (6)Digital PLLs filter jitter from 14 Hz, 28 Hz, 56 Hz, 112 Hz, 224 Hz, 448 Hz or 896 Hz; (7)Automatic hitless reference switching and digital holdover on reference fail; (8)Four reference inputs configurable as single ended or differential; (9)Eight LVPECL outputs and four LVCMOS outputs; (10)Operates from a single crystal resonator or clock oscillator; (11)Configurable via SPI/I2C interface.

Diagrams

|

ZL30100 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ZL30101 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ZL30102 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ZL30102QDG |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ZL30105 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ZL30106 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))