Product Summary

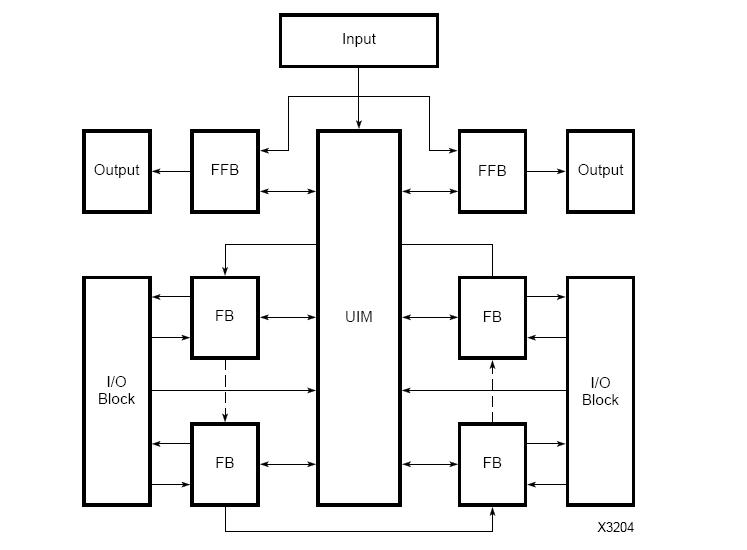

The XC7354-15PC44C is a CMOS EPLD. It employs a unique Dual-Block architecture, which provides high speed operations via Fast Function Blocks and/or high density capability via High Density Function Blocks. Fast Function Blocks (FFBs) provide fast, pin-to-pin speed and logic throughput for critical decoding and ultrafast state machine applications. High-Density Function Blocks (FBs) provide maximum logic density and systemlevel features to implement complex functions with predictable timing for adders and accumulators, wide functions and state machines requiring large numbers of product terms, and other forms of complex logic. In addition, the XC735415PC44C architecture employs the Universal Interconnect Matrix (UIM) which guarantees 100% interconnect of all internal functions. The XC7354-15PC44C provides constant, short interconnect delays for all routing paths through the UIM. Constant interconnect delays simplify device timing and guarantee design performance, regardless of logic placement within the chip.

Features

XC7354-15PC44C features: (1)High-performance Erasable Programmable Logic Devices (EPLDs); (2)Advanced Dual-Block architecture; (3)100% interconnect matrix; (4)High-speed arithmetic carry network; (5)Multiple independent clocks; (6)Each input programmable as direct, latched, or registered; (7)High-drive 24 mA output; (8)I/O operation at 3.3 V or 5 V; (9)Meets JEDEC Standard (8-1A) for 3.3 V±0.3 V; (10)Power management options; (11)Multiple security bits for design protection; (12)Supported by industry standard design and verification tools; (13)100% PCI compliant.

Diagrams

|

XC7300 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC73144 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC7336 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))