Product Summary

The LXT380LE is an octal short haul Pulse Code Modulation (PCM) Line Interface Unit for ITU G.703 2.048Mbit/sec. transmission systems. It incorporates eight independent receivers and eight independent transmitters in a single LQFP-144 or PBGA-160 package. The LXT380LE features a differential data receiver architecture with high noise interference margin and uses peak detection and a variable threshold for reliable data recovery down to 500mV or up to 12 dB of cable attenuation. The fully digital clock recovery PLL is referenced to a low frequency master clock of 2.048MHz. Each receiver incorporates an analog/digital Loss of Signal (LOS) processor. The LXT380LE features a "smart power" driver failure monitoring circuit in parallel to TTIP and TRING that reports secondary line shorts.

Parametrics

LXT380LE absolute maximum ratings: (1)DC supply voltage VCC0, VCC1, TVCC 0-7: -0.5V to 4.0V; (2)DC supply voltage VCCIO0, VCCIO1: -0.5 to 7.0V; (3)Input voltage on any digital pin VIN: GND-0.5 to VCCIO0 + 0.5V; (4)Input voltage on RTIP, RRING1 VIN: GND-0.5 to VCC0 + 0.5V; (5)ESD voltage on any Pin2 VIN: 2000V; (6)Transient latch-up current on any pin IIN: 100mA; (7)Input current on any digital pin3 IIN: -10 to 10mA; (8)DC input current on TTIP, TRING3 IIN: ±100mA; (9)DC input current on RTIP, RRING3 IIN: ±100mA; (10)Storage temperature TSTOR: -65℃ to +150℃.

Features

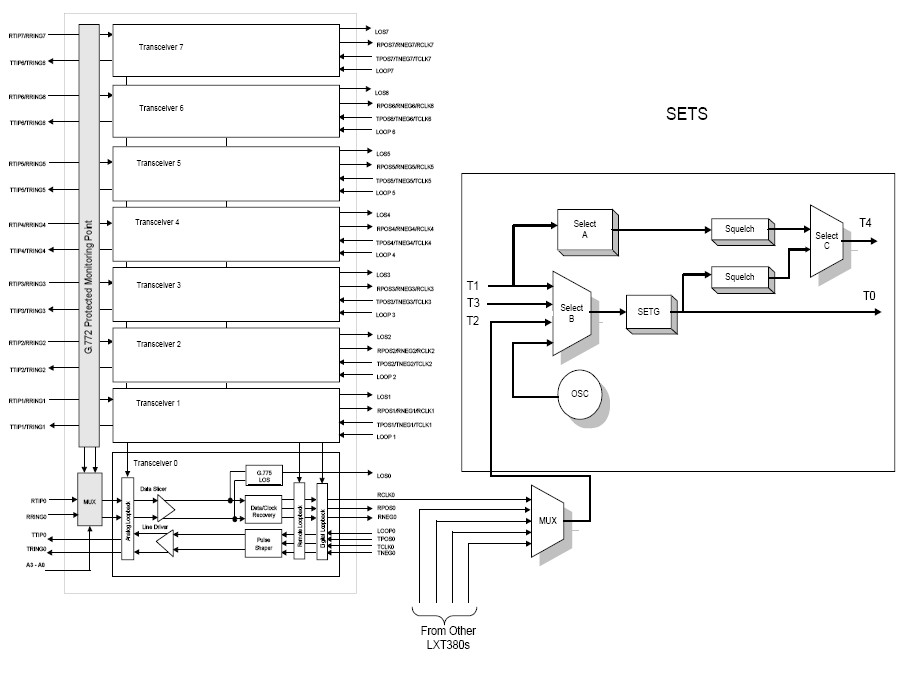

LXT380LE features: (1)Octal E1 short haul transceiver per ITU G.703; (2)Single rail supply voltage of 3.3V with 5V I/O capability; (3)Low power consumption of <100mW per channel (typ.); (4)75Ω/120Ω TX operation without component changes; (5)Hitless Protection Switching (HPS); (6)Driver short circuit current limiter (<50mA RMS); (7)Transmit return loss exceeds ETSI ETS 300166; (8)Selectable transmit pulse shape PLL; (9)Per channel clock recovery; (10)Selectable HDB3 line encoder/decoder; (11)On chip secondary driver short circuit monitoring circuit; (12)Provides protected monitoring points per ITU G.772; (13)Analog/digital and remote loop back testing function; (14)LOS per ITU G.775 and ETS 300 233 (selectable); (15)8 bit parallel or 4 wire serial control interface; (16)JTAG Boundary Scan test port per IEEE 1149.4; (17)Small footprint 144 Pin LQFP & 160 Pin PBGA Packages.

Diagrams

|

LXT307 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LXT312 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LXT313 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LXT335 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LXT350 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LXT351 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))