Product Summary

The IDT82V3255TF is an integrated, single-chip solution for the Synchronous Equipment Timing Source for Stratum 3, SMC, 4E and 4 clocks in SONET / SDH equipments, DWDM and Wireless base station, such as GSM, 3G, DSL concentrator, Router and Access Network applications. The IDT82V3255TF supports three types of input clock sources: recovered clock from STM-N or OC-n, PDH network synchronization timing and external synchronization reference timing. The applications of the IDT82V3255TF include BITS / SSU, SMC / SEC (SONET / SDH), DWDM cross-connect and transmission equipments, Central Office Timing Source and Distribution, Core and access IP switches / routers, Gigabit and Terabit IP switches / routers, IP and ATM core switches and access equipments, Cellular and WLL base-station node clocks, Broadband and multi-service access equipments, Any other telecom equipments that need synchronous equipment, system timing.

Parametrics

IDT82V3255TF absolute maximum ratings: (1)VIH Input Voltage High: 0.7VDD V; (2)VIL Input Voltage Low: 0.2VDD V; (3)PU Pull-Up Resistor: 10 to 80KΩ; (4)IIN Input Current: 250μA; (5)VIN Input Voltage: -0.5V to 5.5V.

Features

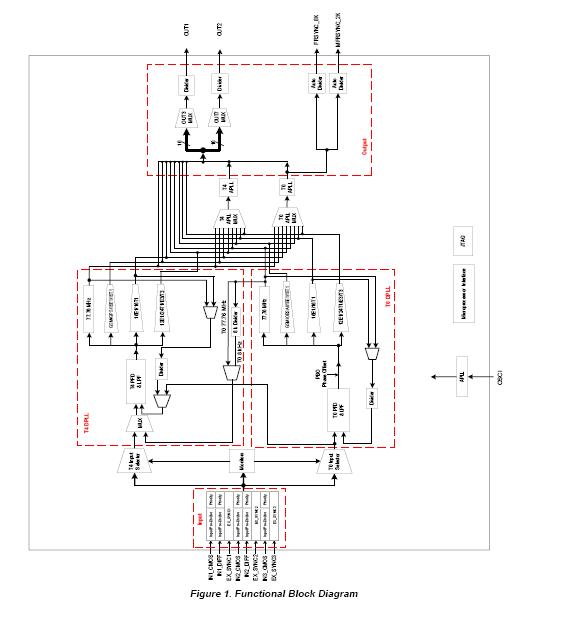

IDT82V3255TF features: (1)Provides an integrated single-chip solution for Synchronous Equipment Timing Source, including Stratum 3, SMC, 4E and 4 clocks; (2)Employs DPLL and APLL to feature excellent jitter performance and minimize the number of the external components; (3)Integrates T0 DPLL and T4 DPLL; T4 DPLL locks independently or; (4)locks to T0 DPLL; (5)Supports Forced or Automatic operating mode switch controlled by; (6)an internal state machine; the primary operating modes are Free-; (7)Run, Locked and Holdover; (8)Supports programmable DPLL bandwidth (0.1 Hz to 560 Hz in 11 steps) and damping factor (1.2 to 20 in 5 steps); (9)Supports 1.1X10-5 ppm absolute holdover accuracy and 4.4X10-8; (10)ppm instantaneous holdover accuracy; (11)Supports PBO to minimize phase transients on T0 DPLL output to; (12)be no more than 0.61 ns; (13)Supports phase absorption when phase-time changes on T0 selected input clock are greater than a programmable limit over an interval of less than 0.1 seconds; (14)Supports programmable input-to-output phase offset adjustment; (15)Limits the phase and frequency offset of the outputs; (16)Supports manual and automatic selected input clock switch; (17)Supports automatic hitless selected input clock switch on clock failure; (18)Supports three types of input clock sources: recovered clock from STM-N or OC-n, PDH network synchronization timing and external synchronization reference timing; (19)Provides three 2 kHz, 4 kHz or 8 kHz frame sync input signals, and a 2 kHz and an 8 kHz frame sync output signals; (20)Provides 5 input clocks whose frequency cover from 2 kHz to; (21)622.08 MHz; (22)Provides 2 output clocks whose frequency cover from 1 Hz to; (23)622.08 MHz; (24)Provides output clocks for BITS, GPS, 3G, GSM, etc.; (25)Supports PECL/LVDS and CMOS input/output technologies; (26)Supports master clock calibration; (27)Supports Line Card application; (28)Meets Telcordia GR-1244-CORE, GR-253-CORE, ITU-T G.812, ITU-T G.813 and ITU-T G.783 criteria.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

IDT82V3255TFG |

|

IC PLL WAN SMC STRATUM 3 64-TQFP |

Data Sheet |

|

|

||||||

|

IDT82V3255TFG8 |

|

IC PLL WAN SMC STRATUM 3 64-TQFP |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))