Product Summary

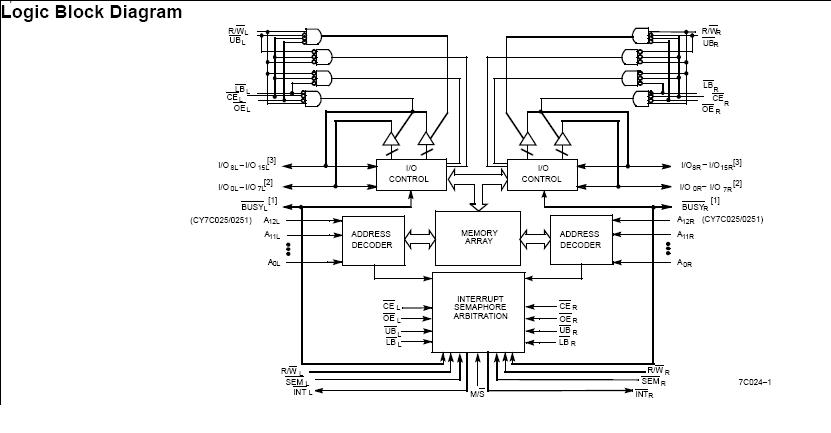

The CY7C024-25AC is a low-power CMOS 4K x 16/18 and 8K x 16/18 dual-port static RAM. Various arbitration schemes are included on the CY7C024-25AC to handle situations when multiple processors access the same piece of data. Two ports provided, permitting independent, asynchronous access for reads and writes to any location in memory. The CY7C024-25AC can be utilized as standalone 16-/18-bit dual port static RAM or multiple devices can be combined in order to function as a 32-/36-bit or wider master/slave dual port static RAM. An M/S pin is provided for implementing 32-/36-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/ graphics memory.

Parametrics

CY7C024-25AC absolute maximum ratings: (1)Storage Temperature:–65℃ to +150℃; (2)Ambient Temperature with Power Applied:–55℃ to +125℃; (3)Supply Voltage to Ground Potential:–0.3V to +7.0V; (4)DC Voltage Applied to Outputs; (5)in High Z State:–0.5V to +7.0V; (6)DC Input Voltage:–0.5V to +7.0V; (7)Output Current into Outputs (LOW): 20mA; (8)Static Discharge Voltage: >2001V (per MIL-STD-883, Method 3015); (9)Latch-Up Current: >200mA.

Features

CY7C024-25AC features: (1)True Dual-Ported memory cells which allow simultaneous reads of the same memory location; (2)K x 16 organization (CY7C024); (3)K x 18 organization (CY7C0241); (4)K x 16 organization (CY7C025); (5)K x 18 organization (CY7C0251); (6)0.65-micron CMOS for optimum speed/power; (7)High-speed access: 15 ns; (8)Low operating power: ICC = 150mA (typ.); (9)Fully asynchronous operation; (10)Automatic power-down; (11)Expandable data bus to 32/36 bits or more using Master/Slave chip select when using more than one device; (12)On-chip arbitration logic; (13)Semaphores included to permit software handshaking between ports; (14)INT flag for port-to-port communication; (15)Separate upper-byte and lower-byte control; (16)Pin select for Master or Slave; (17)Available in 84-pin PLCC and 100-pin TQFP.

Diagrams

|

CY7C006 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXCT |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AC |

|

IC SRAM 16KX8 DUAL 64LQFP |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))